Jun. 2005

文章编号:1672-3767(2005)02-0066-04

# 三种 SoC 片上总线的分析与比较

## 张丽媛1,章 军2,陈新华1

(1. 山东科技大学 信息科学与工程学院,山东 泰安 271019; 2. 中国科学研究院 计算技术研究所,北京 100080)

摘 要:随着以 IP 核复用为基础的 SoC 设计技术的发展,工业界及研究组织正积极从事相关 IP 互联标准方案的制定工作。本文介绍了目前 SoC 设计中常用的三种片上总线标准,即 IBM 公司的 CoreConnect 总线、ARM 公司的 AMBA 总线和 OCP-IP 组织的 OCP 总线,重点分析和比较了它们的特性,并针对它们不同的特点,阐述其合适的应用领域。

关键词:SoC(System-on-Chip);片上总线,IP(Intellectual Property)核;可复用设计

中图分类号:TP 23

文献标识码:A

# The Analysis and Comparison of three SoC On-chip Buses

Zhang Li-yuan<sup>1</sup>, Zhang Jun<sup>2</sup>, Chen Xin-hua<sup>1</sup>

- (1. College of Information Science and Engineering, SUST, Taian, Shandong 271019, China;

- 2. Institute of Computing Technology, Chinese Academy of Sciences, Beijing 100080, China)

Abstract: With the development of SoC design technology based on IP core re-usability, people in the industrial sector and research institutes are devoting themselves to stipulation of IP interconnection standard. At present, three typical on-chip bus specifications, such as CoreConnect of IBM company, AMBA of ARM company, OCP of OCP-IP organization are usually used in SoC design. Their features are analyzed and compared and finally, their applied domains are presented accordingly.

Key words: SoC(System-on-Chip); on-chip bus; IP(Intellectual Property) core; reusable design

目前,片上系统 SoC(System-on-Chip)已经成为 IC 业界的焦点,基于 IP(Intellectual Property)核集成的可复用设计技术受到了高度重视,而可复用设计技术的关键在于建立正确、高效、灵活的OCB(on-chip bus,片上总线)标准<sup>[1,2]</sup>。OCB 标准化有利于大量 SoC 问题的解决,包括 IP 芯核可移植性、设计可复用性、充分利用公共外设核处理器、改进自动验证,以及提高从公共设计平台创建产品的定制化能力。

片上总线一般分为系统总线(System Bus)与外围总线(Peripheral Bus)两种类型。系统总线用来互连高性能 IP 模块,这些模块包括嵌入式 CPU(即 MCU)、DSP、主存控制器、DMA 控制器等。它的特点是带宽要求高、实时响应速度快;外围总线用来互连性能低、功耗低的设备,是为了满足功耗、便携性、可重用性等方面的特殊要求。系统总线与外围总线之间通过总线桥相连。由于总线桥连接的两条总线的时钟可能不同,所以必须在总

线桥设计中解决异步握手与数据流水等问题。总 线上的 IP 模块分为主模块(Master)和从模块 (Slave)两类。

目前,国际上比较成熟的标准化、开放化的片上总线标准有 IBM 公司的 CoreConnect 总线<sup>[3]</sup>、ARM 公司的 AMBA 总线<sup>[4]</sup>、OCP - IP(Open Core Protocol International Partnership)设计的 OCP 总线<sup>[5]</sup>。介绍并比较这三种典型的总线标准,并针对它们不同的特点,给出其合适的应用领域。

## 1 CoreConnect 总线

CoreConnect 总线规范<sup>[3]</sup>是 IBM 公司设计的一种片上系统总线协议,它使处理器、内存控制器和外设在基于标准产品平台设计中的集成和复用更加灵活,从而提高了整个系统的性能。

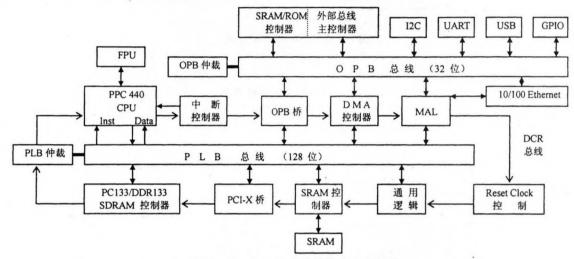

CoreConnect 总线规范包括三种总线和一个连接高性能总线与低性能总线的桥,即 PLB(processor local bus)、OPB(on-chip peripheral bus)、

DCR(device control register bus)和 OPB 桥。图 1是 CoreConnect 在一个 SoC 设计中的总线结构图。

CoreConnect 的 PLB 总线是一个高性能总线,通过总线接口单元来访问存储器设备<sup>[6]</sup>,如图 1中所述。如 PowerPC440 CPU 核、PCI - X 桥、PC133/DDR133 SDRAM 控制器等性能高带宽宽的设备都连接在 PLB 上。

CoreConnect 的 OPB 总线为连接具有不同的 总线宽度及时序要求的外设和存储器提供了一条 途径,并尽量减小对 PLB 性能的影响。一些低性 能设备都连在 OPB 上。在 PLB 与 OPB 之间有一个 OPB 桥,用来完成 PLB 主设备与 OPB 从设备 之间的数据传输。

CoreConnect 的 DCR 总线主要用来在各种 PLB 和 OPB 的主、从设备中配置状态寄存器和控制寄存器,这就使 PLB 从低性能状态中减小负荷,更有效地控制读写传输。 DCR 总线在内存地址映射中取消了配置寄存器,减小取操作,增加处理器内部总线的带宽<sup>[6]</sup>。 CoreConnect 内部三种总线性能描述见表 1。

图 1 CoreConnect 总线结构应用实例图

Fig. 1 Practical example in application of core connect based system-on-a-chip

### 表 1 CoreConnect 总线性能描述

Tab. 1 Description of CoreConnect bus performance

| 总线名称         | CoreConnect<br>PLB                                    | CoreConnect<br>OPB                      | CoreConnect<br>DCR |

|--------------|-------------------------------------------------------|-----------------------------------------|--------------------|

| 数据线宽度<br>(位) | 32 - 64 -<br>128 - 256 -                              | 8 - 16 -<br>32 -                        | 32 -               |

| 地址线宽度<br>(位) | 32 -<br>(地址流水作业,<br>减少延迟)                             | 32 -                                    | 10 -               |

| 体系结构         | 主设备<br>(最大8个)<br>/从设备<br>仲裁优先级                        | 多主/从设备<br>仲裁优先级<br>动态控制<br>总线大小         | _                  |

| 数据线协议        | 单一的读/写传输<br>支持流水/<br>分裂/猝发传输<br>字节/半字/字<br>特殊的 DMA 方式 | 单一的读/写传输<br>支持猝发传输<br>字节/半字/字<br>支持重试操作 | * <u>-</u>         |

| 时序           | 同步                                                    | 同步                                      | -                  |

| 互接           | 多路                                                    | 多路                                      | 多路                 |

| 支持互接         | 不支持三态<br>总线独立的读<br>/写数据线                              | 不支持三态<br>总线独立的读/<br>写数据线                | -                  |

### 2 AMBA 总线

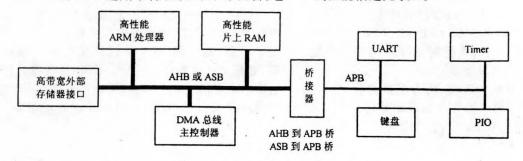

AMBA (Advanced Microcontroller Bus Architecture) 总线规范<sup>[4]</sup>是 ARM 公司设计的一种用于高性能嵌入式系统的总线标准。它独立于处理器和制造工艺技术,增强了各种应用中的外设和系统宏单元的可重用性,该规范引入的先进高性能总线(AHB)是现阶段 AMBA 实现的主要形式。AMBA 总线也是一个多总线系统。规范定义了三种可以组合使用的不同类型的总线: AHB (Advanced High - performance Bus)、ASB (Advanced System Bus)和 APB (Advanced Peripheral Bus)。典型的基于 AMBA 的 SoC 核心部分如图 2 所示。

AMBA的 AHB 适用于高性能和高时钟频率的系统模块。它作为高性能系统的骨干总线,主要用于连接高性能和高吞吐量设备,如 CPU、片上存储器、DMA 设备和 DSP 或其它协处理器等。AHB 的关键是对接口和互连均进行定义,目的是在任何工艺条件下实现接口和互连的最大带宽。

AMBA 的 ASB 适用于高性能的系统模块。 在不必要适用 AHB 的高速特性的场合,可选择 ASB 作为系统总线。它同样支持处理器、片上存储器和片外处理器接口与低功耗外部宏单元之间 的连接。其主要特性与 AHB 类似,主要不同点是 它读数据和写数据采用同一条双向数据总线。

AMBA 的 APB 适用于低功耗的外部设备,它

已经过优化,以减少功耗和对外设接口的复杂度; 它可连接在两种系统总线上。AMBA 内部三种总 线性能描述见表 2。

图 2 基于 AMBA 的微控制器

Fig. 2 AMBA based microcontroller

表 2 AMBA 总线性能描述 Tab. 2 Description AMBA bus performances

| 总线名称     | AMBA AHB(新一代总线)                                      | AMBA ASB(第一代总线)                       | AMBA APB                      |

|----------|------------------------------------------------------|---------------------------------------|-------------------------------|

| 数据线宽度(位) | 32 - 64 - 128 - 256 -                                | 32 - 64 - 128 - 256 -                 | 8 - 16 - 32 -                 |

| 地址线宽度(位) | 32 -<br>(地址流水作业,减少延迟)                                | 32 -                                  | 32 –                          |

| 体系结构     | 多主/从设备<br>仲裁机制                                       | 主/从设备<br>仲裁机制                         | 单主设备(桥)/多从设备<br>无仲裁           |

| 数据线协议    | 单一的读/写传输<br>支持流水/分裂传输<br>支持猝发传输(4,8,16 拍)<br>字节/半字/字 | 单一的读/写传输<br>支持流水/猝发传输<br>字节/半字/字<br>一 | 一次读/写传输占<br>两个时钟周期<br>不支持猝发传输 |

| 时序       | 同步                                                   | 同步                                    | 同步                            |

| 互接       | 多路                                                   | 没有定义                                  | 无定义                           |

| 支持互接     | 不支持三态总线<br>分开的读/写数据线                                 | 三态总线<br>单一的读/写 <b>数据</b> 线            | 不支持三态总线<br>分开的读/写数据线          |

## 3 OCP 总线

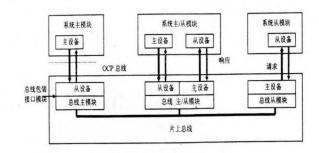

OCP(Open Core Protocol)标准<sup>[5]</sup>是 OCP - IP 设计的一个规范。它是为了在 SoC 设计中实现 IP 核的即插即用而制订的片上总线规范,不依赖于特定处理器内核的总线协议。只要 IP 核和总线符合 OCP,即使更换处理器内核和总线,也不需要重新设计 IP 核,应用非常灵活。

OCP 与 VSIA (Virtual Socket Interface Alliance)公司的 VCI (Virtual Component Interface)非常类似。VCI 只定义了 IP 核通信中数据流方面的内容,而 OCP 更像是 VCI 的功能扩展集,OCP 把所有的内核通信统一成一个整体,包括边频控制、检测动力信号等,它的同步单向信号大大简化了 IP 核的实现、综合和时序分析。OCP 标准是目前唯一一个无所有权,公开许可,并给出 IP 核系统级综合要求的以核为中心的协议,克服了反复定义、校验、证明和兼容接口的复杂性。图 3 为一个简单系统,包括一个包装总线和三个 IP 核实

体。

IP核的性质决定了它是否需要主从设备,接口包装模块是作为 OCP 连接实体的补充部分。一次系统传输过程如下:一个系统 OCP 主设备向它所连接的从设备(总线包装接口模块)发送命令、控制或者数据,接口模块向片上总线系统提出请求,OCP并没有实现嵌入式总线的功能,它是将 OCP 的请求转换成嵌入式总线操作来传输,接收总线包装接口模块(作为 OCP 主设备)再将这个嵌入式总线操作转换成一个合法的 OCP 命令,OCP 从设备接收这个命令并执行。这就完成了一次传输过程。

## 4 三种片上总线的比较

以上介绍的三种总线都是完全同步的设计, 都是使用时钟的上升沿来驱动和采样信号的。最 大的区别在于他们提供的特性和规范的完整性不 同<sup>[6]</sup>。三种总线的特性比较如表 3 所列。

#### 表 3 三种总线特性比较

Tab. 3 Comparisons of performance of three buses

| 总线名称        | CoreConnect | AMBA     | OCP                        |

|-------------|-------------|----------|----------------------------|

| 互连方式        | 共享总线        | 共享总线     | 点对点                        |

| 主控制器        | 多个          | 多个       | 单个                         |

| 数据线宽度<br>/位 | 32 - 256    | 32 – 256 | 用户可配置                      |

| 地址线宽度       | 32          | 32       | * 8                        |

| 数据传输        | 字节/半字       | 字节/半字    | 字节/半字                      |

| 方式          | /字          | /字       | /字                         |

| 事务传输        | 流水/分裂       | 流水/分裂/   | 流水/                        |

| 方式          | /猝发传输       | 猝发传输     | 猝发传输                       |

| 数据对齐        | 大端对齐/       | 大端对齐/    | 大端对齐/                      |

| 方式          | 小端对齐        | 小端对齐     | 小端对齐                       |

| 仲裁机制        | 系统定义        | 系统定义     | 无仲裁                        |

|             | 硬件技术/       | 硬件技术/    | 完全独立于<br>系统设计/<br>IP 核类型无线 |

| wh as M.    | IP 核类型/     | IP 核类型/  |                            |

| 独立性         | 综合工具        | 综合工具     |                            |

|             | 无关          | 无关       |                            |

图 3 OCP 应用实例图

Fig. 3 Sketch of practical example in application of OCP

CoreConnect 拥有完备的一整套技术文档,在技术上可行性较强,可以应用在类似于工作站的高性能系统的连接,可以适用于未来更庞大、更复杂的系统连接,IBM 声称免费,但需要授权协议; AMBA 总线规范拥有众多第三方支持,被 ARM 公司 90% 以上的合作伙伴采用,在基于 ARM 处理器内核的 SoC 设计中,已经成为广泛支持的现有

#### 表 4 三种总线应用综合比较

Tab. 4 Comparisons of application of three buses

|   | 总线名称 | CoreConnect       | AMBA                   | OCP                       |

|---|------|-------------------|------------------------|---------------------------|

|   | 适用器件 | FPGA, PLD, ASIC   | FPGA, PLD, ASIC        | FPGA, PLD, ASIC           |

|   | 应用范围 | 高性能嵌入式系统          | 高性能嵌入式系统               | 高性能嵌入式系统小型嵌入式系统           |

|   | 可用资源 | 完备的技术文档丰富的 IP 核资源 | ARM 合作伙伴众多,提供了丰富的 IP 核 | 对 IP 核没有特殊要求,而且提供丰富的 IP 核 |

| M | 价格   | IBM 声称免费,但需要授权协议  | ARM 声称免费,但需要授权协议       | 完全免费                      |

互联标准之一,适合较复杂的应用,需要遵守较简单的操作协议, AMBA 的使用也需要授权协议; 而完全免费的 OCP 总线是一个完全独立的、真正以核为中心的总线,不依赖特定的系统要求,使用方便,最好地实现了 IP 核的复用,对系统的要求最低,适合较简单的应用,还可以嵌入在 CoreConnect 和 AMBA 中用。基于三种总线的特性,可以得出其应用的综合比较,如表 4 所列。

## 5 结束语

本文对 SoC 中常用的三种总线 CoreConnect、AMBA 和 OCP 的特性进行了详细分析和比较,阐述了各自的应用范围,为 SoC 设计中总线的选择提供了参考。SoC 系统中总线的选择不仅要看其性能,还要看其应用范围,是否有足够的 IP 核资源可用等等。SoC 中可以选用的总线还有很多,如 Altera 的 Avalon、Silicore Corp 的 Wishbone、Plamchip 的 CoreFrame、Mentor Graphics 的 FISPbus等。各有其特点和适用领域。在 SoC 中选用片上总线时,要进行认真考虑,仔细权衡。

#### 参考文献:

- [1] A. Rincon, W. Lee and M. Slatery. The Changing Landscape of System - on - Chip Design [R]. IBM MicroNews, 3rd Quarter 1999, Vol. 5, No. 3, IBM Microelectronics

- [2] Sudeep Pasricha, Mohamed Ben Romdhane and Nikil Dutt. High Level Design Space Exploration of Shared Bus Communication Architecture [R]. CECS Technical Report #04 - 06, University of California, Irvine CA 92697, Mar 13,2004.

- [3] IBM Corp. The CoreConnect Bus Architecture [EB/OL]. http://www-306.ibm.com/chips/techlib/techlib.nsf/ productfamilies/CoreConnect\_Bus\_Architecture.

- [4] ARM Corp. The AMBA Specification Rev 2. 0 [EB/OL]. http://www.arm.com/products/solutions/AMBA\_Spec.html.

- [5] OCP IP. OCP Specification Rev 2. 0 [EB/OL]. http://www.ocpip.org/socket/ocpspec/.

- [6] Patrick Pelgrims, Tom Tierens and Dries Driessens. Overview AMBA Avalon CoreConnect Wishbone [EB/OL]. http://www.opencontent.org/openpub/.